- IC�ͺ�

��������ԿƼ�����˾

- Ӫҵִ�գ�δ�����Ӫģʽ�����������ڵ������㶫 ������ҵ��վ��

http://www.yihuidzic.com/

�ղر���˾ ������536424

��ϵ��ʽ

- ��ַ��������������·3039�Ź����Ļ�����1627

- ��ϵ�ˣ�Ҷ��

- �绰��0755-83031949

- ���棺0755-83689445

- �ֻ���13590108836

- QQ��

- E-mail��2851397780@qq.com

��Ʒ����

���ɵ�·(IC)(7)��ԴIC(2)������(6)���Ӳ���(3)����δ����(2)

IC

- ����IC(7)

- ��ѹIC(2)

- ����������(1)

- ������ѹ��(��)(5)

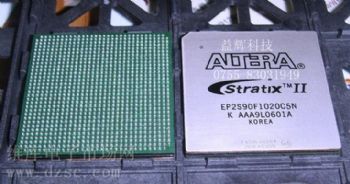

��ӦEP2S90F1020C5N��ԭװEP2S90F1020C5N

- ��Ʒ�۸�

- ��-/ 1pcs

��-/ 10pcs

��-/ 100pcs

- �� �ң�

- ALTERA

- �� װ��

- BGA

- �� �ţ�

- 06+

- �� ����

- 2500

��Ʒ��ѯֱ�ߣ�0755-83031949

��Ʒ��ϸ˵��

EP2S90F1020C5N����/Ŀ¼��Ϣ

������Ӧ��Altera

������ɵ�·(ic)

������/Ԫ�� 90960

��װ/��� 1020- FBGA��װ

�����¶�0��C ~ 85��C

��Դ��ѹ1.14 V ~ 3.465 V

��Ǧ״̬:��Ǧ

RoHS״̬����

��������EP2S90F1020C5N

EP2S90F1020C5N544

Features The Stratix II family offers the following features:

�� 15,600 to 179,400 equivalent LEs; see Table 1�C1

�� New and innovative adaptive logic module (ALM), the basic

building block of the Stratix II architecture, maximizes performance

and resource usage efficiency

�� Up to 9,383,040 RAM bits (1,172,880 bytes) available without

reducing logic resources

�� TriMatrix memory consisting of three RAM block sizes to implement

true dual-port memory and first-in first-out (FIFO) buffers

�� High-speed DSP blocks provide dedicated implementation of

multipliers (at up to 450 MHz), multiply-accumulate functions, and

finite impulse response (FIR) filters

�� Up to 16 global clocks with 24 clocking resources per device region

�� Clock control blocks support dynamic clock network enable/disable,

which allows clock networks to power down to reduce power

consumption in user mode

�� Up to 12 PLLs (four enhanced PLLs and eight fast PLLs) per device

provide spread spectrum, programmable bandwidth, clock switchover,

real-time PLL reconfiguration, and advanced multiplication

and phase shifting

��ز�Ʒ����>>

-

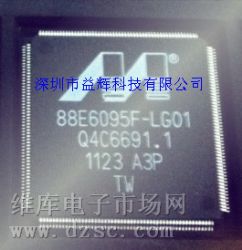

- ��Ӧ88E6095FA3-LGO1C000

- ��55.0

-

- ��Ӧ88F5281-D2-BF02C000

- ��55.0

-

- ��Ӧ88AP270MA2-BHE1C520

- ��55.0

-

- ��ӦXC4036XLA-09HQ240C

- ��55.0

-

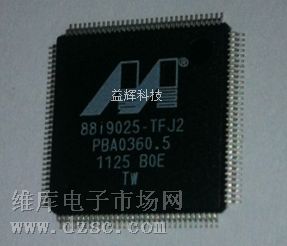

- ��Ӧ88I9025

- ��55.0

-

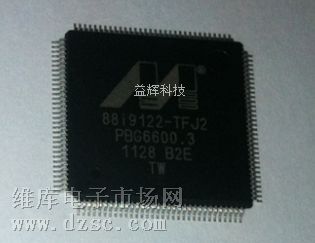

- ��Ӧ88I9122-B2-TEJ2C000

- ��55.0

-

- ��Ӧ88DE2750

- ��55.0